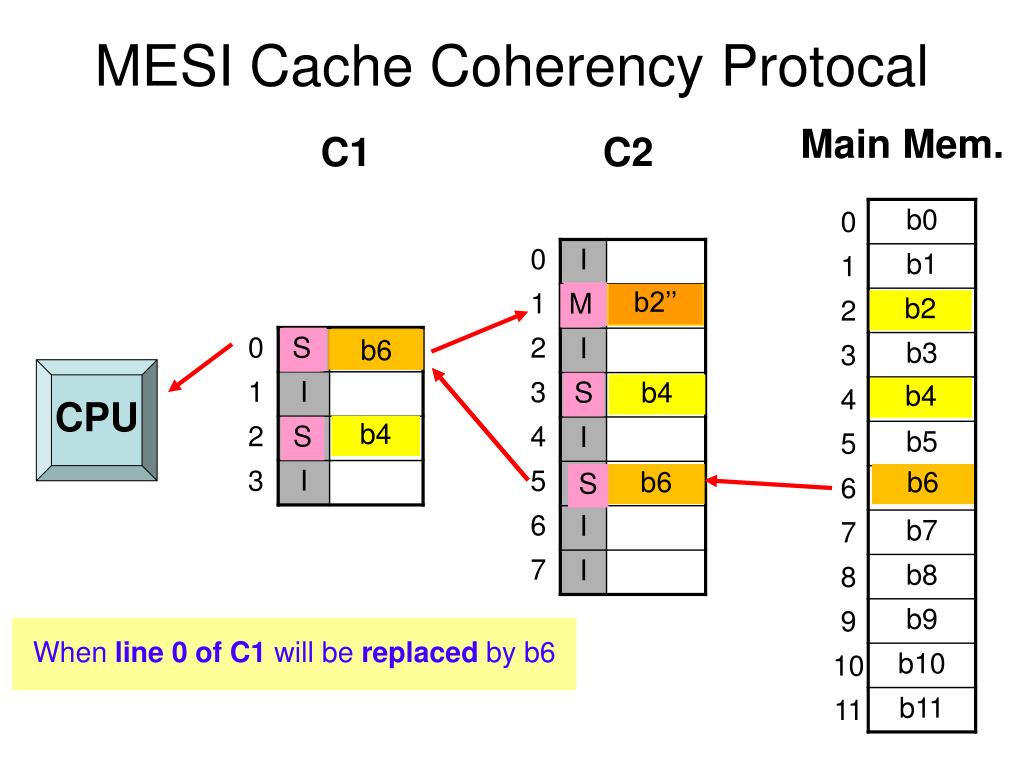

For example, a CPU might prefetch a read or might delay a write out of order. But in practice it's not because while MESI makes the memory caches coherent, modern CPUs have other optimizations that create the same kinds of problems. This could be true at the hardware/assembler level. Thus, if value is not in a register but in cache or main memory, MESI would do its work to make threads see correct values of globals. And it's not true for things like Java where volatile has specific language semantics that have nothing to do with registers. It's certainly not true in C/C++ where volatile is for things like signals not multithreading (at least on platform's with well-defined multi-threading APIs). I know of no language where this is true. When using global variables, which are read and written by several threads, volatile type specifier is used to prevent unwanted optimizations as well as to prevent caching in registers (not in L1-3 caches). (Think about the topology of the cores and the memory controller, that would be insane.) If data is in one core's L2 cache and has to get to another core's L2 cache, it doesn't go over the memory. But today, most laptop/desktop multi-core CPUs have on die memory controllers, so the bus that connects to memory only connects to memory. This used to be true for some multi-chip CPU designs before CPUs had on-chip memory controllers. You could mean that for CPUs without an 元 cache, the L2 inter-cache MESI traffic occurs on the same CPU bus as the one that connects to main memory. Memory isn't a cache and so has no need to participate in the MESI protocol. I'm not sure what you're trying to say here, but it doesn't seem to correspond to anything true. These are sophisticated optimizations though.įor several processors (with no shared 元), MESI operates via Main Memory.

This can reduce the amount of snooping needed. For example, if the 元 cache is inclusive and holds everything in any CPU's L1 or L2 caches, then just knowing that something isn't in the 元 cache is enough to know it's not in any other core's cache. In some processor designs, the 元 cache serves as an efficient "switchboard" between cores. For several cores of a single processor, MESI operates via 元 cache which is shared among cores of a processor.

0 kommentar(er)

0 kommentar(er)